最大1000万IOPS、100GB/sのスループット、平均100マイクロ秒の遅延を実現するまさに怪物的なスペックを誇るラックスケールフラッシュアレイ「DSSD D5」。DSSDのファウンダーであるジェフ・ボンウィック氏にDSSDの開発経緯やテクノロジーについて聞く。

DSSD共同創立者兼CTO ジェフ ・ボンウィック氏

CPUは2万倍速くなっているのに、IOPSは10倍というギャップ

今回インタビューしたDSSD CTOのジェフ・ボンウィック氏は、もともとサン・マイクロシステムズでZFSの開発を主導してきた人物で、2010年にアンディ・ベクトルシャイム氏とともに最高級のフラッシュアレイを作るべく、DSSDを立ち上げた。その後、2014年にEMCが製品開発中のDSSDを買収。2016年3月にいよいよ未曾有のパフォーマンスを誇るラックスケールフラッシュ「DSSD D5」が登場した。

DSSDが目指したのは、CPUの計算速度に追いつくI/Oのパフォーマンスを実現することだ。ボンウィック氏は、「フラッシュが使われ始めた頃、多くの人はそのパフォーマンスに驚いた。同時に、フラッシュのパフォーマンスをどうやれば引き出せるかをみんな考えた」と語る。

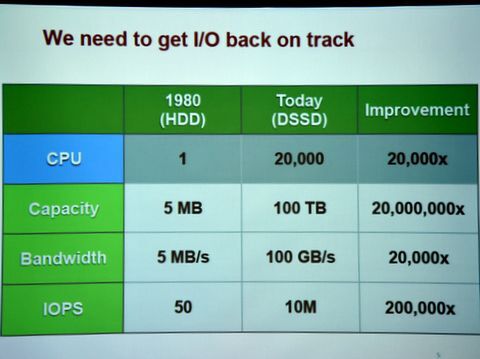

コンピューターの処理は、計算速度とデータのI/Oを両面で考えなければならない。1980年代と比較すると、CPUに関しては約2万倍高速になっているが、I/Oに関してはそこまで大きな伸びが見られないという事実がある。「キャパシティは10万倍になっているが、帯域は100倍、IOPSは10倍しか伸びていない。HDDはディスクアームが1つしかないので、IOPSには限界がある」とボンウィック氏は指摘する。もちろん、帯域に関しても問題があり、セクタあたりの密度を増やしても、帯域が拡大しなければ、性能はリニアに拡大しない。

CPUの性能向上に対して、ストレージのI/Oは伸び悩んでいる

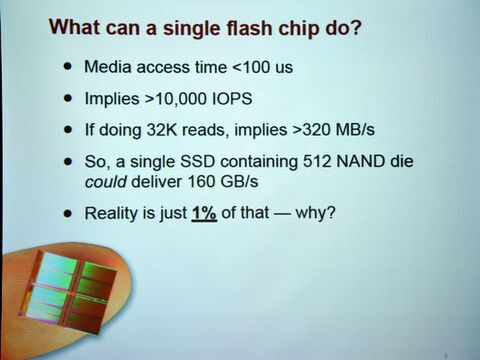

高速なフラッシュの登場はこうしたI/Oの問題を一気に解消する潜在能力を秘めていた。実際、2010年に同社が入手したNANDのスペックを見ると、メディアのアクセスタイミングは100マイクロ秒未満に抑えられており、IOPSは10万を実現していた。「32KBリードであれば、320MB/sを実現できるため、512のNANDチップを搭載したSSDであれば、計算上は160GB/sというスループットが可能になる」(ボンウィック氏)と見込まれた。しかし、実際はこの1%しか達成されなかったという。なぜだろうか?

NANDの性能を引き出せないのはなぜか?

フラッシュの本来の性能を引き出せないのはなぜか?

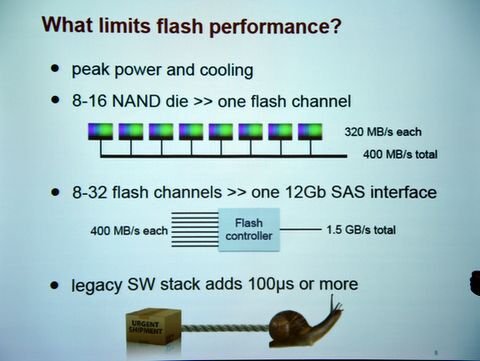

ボンウィック氏は、いくつかの制限を指摘する。まずはピーク時の電力と冷却に問題があり、DSSDのフォームファクタで限界があったのが1つ。また、帯域の問題も大きかった。通常、8~16のNANDダイで1つのフラッシュチャネルを共有するため、NANDダイごとで320MB/sのIOPSでも、トータルでは400MB/sにしかならなかったという。さらにフラッシュのコントローラーもSASインターフェイスで接続する限り、NANDを複数束ねてもSASの1.5GB/sが最高値となってしまう。ボトルネックにだらけで、スループットにつながらないのが大きな問題だった。

フラッシュのパフォーマンスを阻害する要因

フラッシュの性能を引き出すため、DSSDでは2つのアプローチを考えた。1つはHDDをSSDに置き換えたハイブリッドやオールフラッシュアレイだ。こちらはRAIDや高可用性などエンタープライズのストレージの機能を提供でき、導入や利用も容易だが、ネットワークやI/Oのボトルネックが課題になる。もう1つがPCIeのフラッシュをサーバーに直結する方法だ。こちらはホスト自体にフラッシュを差し込んでしまうため、パフォーマンスは高い。しかし、サーバー間でデータを共有できず、高可用性やスケーラビリティを満たすことができないという。

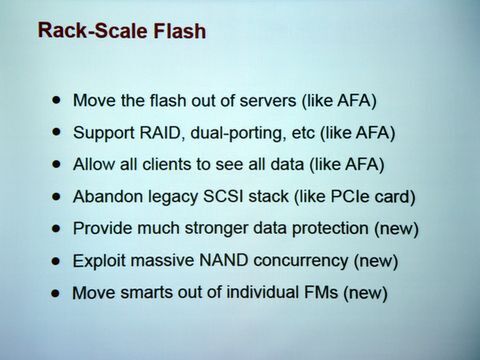

そこで、両者をいいとこどりした新しいラックスケールフラッシュという概念が生まれた。オールフラッシュアレイのようにフラッシュを外付けにし、クライアントから共有できるようにした上で、RAIDやデュアルポートなどにも対応した。一方で、PCIeでサーバーとフラッシュを直結することで、レガシーのSCSIプロトコルに依存しないようにした。さらに強力なデータ保護、NAND単位の管理や同時利用(コンカレンシ)などを追加し、エンタープライズでの利用に耐えうる機能を実装することにしたという。

サーバー直結型フラッシュとオールフラッシュアレイのいいとこどりをしたラックスケールフラッシュ

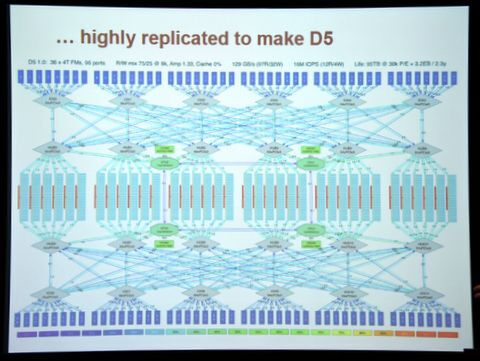

こうしたDSSDのベーシックなハードウェアデザインは、I/OのほとんどをPCIe上で行なうというものだ。クライアントからCPUへの論理的なリクエスト、CPUからフラッシュへの物理的なリクエスト、そしてフラッシュからクライアントへのデータ転送(DMA)をすべてPCIeスイッチ経由で行なう。そして、このうちデータ転送はCPUを一切介さず、すべてカットスルーラリーで行なわれるため、遅延はきわめて小さい。このベーシックデザインを元に、48個のクライアントポートと36個のフラッシュモジュール、4つの物理CPUをフルメッシュ状に接続した巨大なPCIeのファブリックがDSSD D5のバックプレーンになる。

各コンポーネントをフルメッシュ接続したPCIeスイッチのファブリック