ハイエンド向けの

Polaris 11

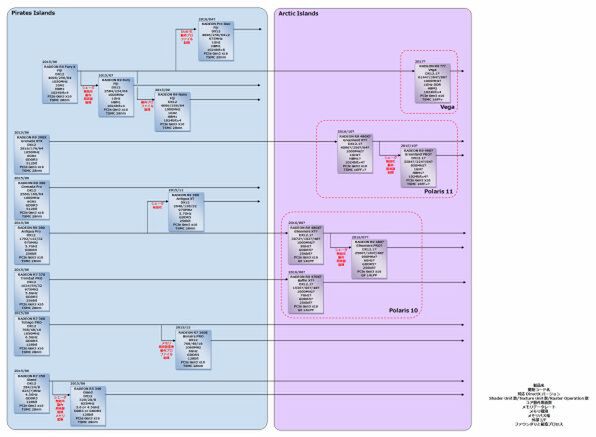

次がPolaris 11の話である。前回のロードマップではここにHBM2を「?」付きで入れたのだが、先のRaja Koduri氏のスライドからここがHBM1でほぼ確定したことになる。

実際のところHBM2のままでは、4チップではやや帯域が過剰すぎ、一方1/2チップだと容量的に不足があったので、HBM1のままというのは理に適っている。

強いて言えばハイエンド品が4GBのままでいいのか? というあたりだが、本命はより大容量のチップが利用可能なHBM2を採用したVega世代が2017年に登場するので、それまでのつなぎと考えれば妥当な戦略だろう。なお、Vega世代が登場するとPolaris 11がミドルレンジ~メインストリームになり、Polaris 10がメインストリーム~ローエンドに移動する形になる。

ちなみにPolaris 10/11世代の共通の特徴、つまりGCN世代との大きな違いの1つは、より広帯域なメモリーシステムへの対応と思われる。下の画像はFijiコアの内部構造図である。

64個のCU(Computation Unit)が2次キャッシュ経由でMC(Memory Controller)を挟んでHBMにアクセスする形になっている。問題はこの2次キャッシュとMCの間のつなぎ方である。

Hawaii/Grenadaコアの場合、8つのメモリコントローラーの先に、各々独立した32bitのGDDR5メモリーが接続されていた。GDDR5の場合、8nプリフェッチ(1回読み込み命令を出すと連続した8つのアドレス分のデータがやってくる)方式なので、1回のメモリーアクセス毎に32bit×8=32Bytes単位で読み取れることになっていた。

ところがHBM1の場合、プリフェッチこそ2nであるが、メモリバス幅は512bitとなる。もっと正確に言えば、HBM全体のメモリーバス幅は1024bitであるが、内部は8つのチャネルに分割されており、それぞれ128bit幅となっている。

したがって、このうちの1チャネルだけを使えば1回の読み取りサイズは128bit×2=32Bytesとなるのだが、実際には8chが2つのMCに接続されているので、1つのMCからはまとめて512bit分のアクセスをすることになり、結局512bit×2=128Bytes単位でのアクセスになってしまう。つまり32Bytes読み込もうとすると128Bytesやって来ることになり、96Bytes分無駄が出てしまう。

これを避けるには、2次キャッシュから128Bytes単位でアクセスするようにすればいいのだが、これを変更すると今度はCUと2次キャッシュの間のアルゴリズムの変更も必要になってしまう。最終的にはCUが、もっと大きな単位でのメモリーアクセスを許容するような構成にする必要がある。

先ほど「技術的にはGDDR5Xを採用する可能性もある」と書いたのはまさにこの点である。GDDR5Xは16nプリフェッチを採用するので、1回のメモリーアクセスあたり64Bytesが読み込まれる。ただPolarisが仮に128Bytesだけでなく64Bytesも許容するような作りになっていれば、技術的にはGDDR5Xでも性能を引き出すことは容易だろう。

ということで、前回のロードマップからの変更点はそれほどないのだが、AMDのGPUアップデートをお届けした。来週はNVIDIAのアップデートをお届けする予定だ。

この連載の記事

-

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 -

第757回

PC

「RISC-VはArmに劣る」と主張し猛烈な批判にあうArm RISC-Vプロセッサー遍歴 - この連載の一覧へ