今回のスーパーコンピューターの系譜は、BBN Technologyが作り上げた2つのコンピューターを取り上げる。このマシンが、その後さまざまな超並列システムに影響を与えることになる。

音響関係のコンサルタント会社が

コンピューターに傾倒

BBN Technologyという会社は1948年に設立された。創立したのはマサチューセッツ工科大学の教授であったRichard Bolt博士とLeo Beranek博士で、後にBolt博士の教え子だったRobert Newman博士も加わる。

当初は“Bolt and Beranek”なる、そのままの名前だったが1950年にNewman博士の加入にあわせて社名をBBN(Bolt, Beranek and Newman)に改名した。

画像の出典は“IEEE Annals of the History of Computing Vol. 27, No. 2”。

Bolt博士とBeranek博士は共にマサチューセッツ工科大学で音響学に携わっており、Bolt and BeranekもBBNも、当初の仕事は音響関係のコンサルタントであった。

具体的には、さまざまなホールの音響設備の設定から、航空機のノイズ分析、録音テープの解析など、音響と名がつくものはなんでも……は言い過ぎにしても幅広い分野の分析や解析のビジネスを手がけており、ビジネス規模もどんどん大きくなっていった。

1948年に立ち上げたときは、マサチューセッツ工科大学の敷地の一部でひっそりと始めたのが、1949年に手狭になり外部に移転。1951年にもう一回引越しをし、数年後には引越し先のビル全体を占めるに至る(その後1957年にも引越し)。

ロサンゼルスにもオフィスを開設したが、ここもあっというまにビル全体を専有したとか。1956年の時点で、フルタイムの従業員50人以外にパートタイム従業員多数がいたというから、けっこう盛況だったようだ。

BBNに1957年に加わったのがJ.C.R.Licklider博士である。Licklider博士も音響学の専門家である。ところが彼はむしろコンピューターに傾倒しており、会社の方向もこれに向けて次第に変わっていく。

1960年にはDECのPDP-1の初号機を購入し、これを改造して4ユーザーで利用できるTime Shareing Systemを構築。これをベースにした電子カルテシステムをマサチューセッツ総合病院に納入するという、音響とは違う方向に振れていく。

特に1962年にからLicklider博士がARPA(Advanced Research Projects Agency:高等研究計画局)に引っ張られ、Information Processing Techniques Officeの長を務めることになってから、方向性が明確に変わってきた。

Licklider博士は最終的に1964年にARPAから離れるが、博士が示したビジョンを具現化する形でARPANETの構築が始まる。

3種類の筐体をケーブルでつないだ

「Pluribus」

1968年9月に、総額100万ドルでIMP(Interface Message Processor:今で言うところのルーター)の提案依頼書がARPAより提示された。当時BBNは本業である音響コンサルティングの分野でもすでにコンピューターを使い始めていたうえ、Licklider博士の影響もあってさまざまな開発を行なっていたこともあり、BBNはこのIMPの開発契約を獲得した。

この第1世代のIMPは、Honeywell 316/516というミニコンピューターをベースとしたシステムで構築され、論文によれば35以上のサイトにこのHoneywellベースのIMPがインストールされた。

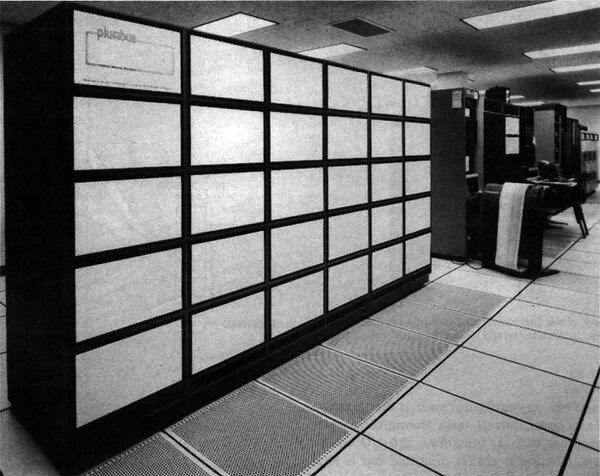

ただARPANETは急速に拡大しつつあり、必要となるIMPの数はまだまだ増えるうえ、より高い性能が求められるようになった。そこで同社は、Honeywell 316/516より安価で、かつより高い性能を持つIMP用のシステムを自社開発することにした。これがBBN Pluribusである。

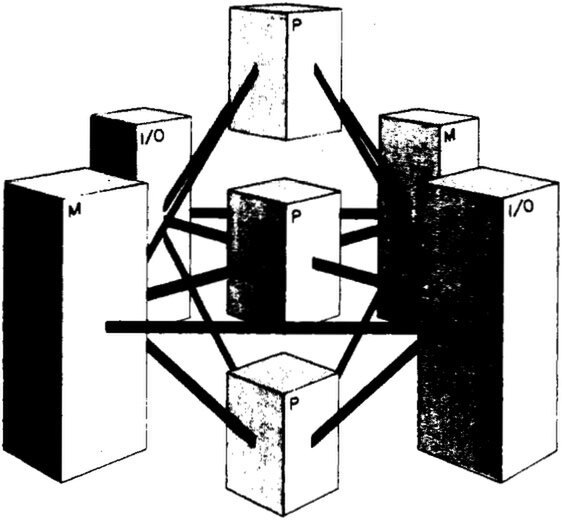

パケット処理という観点では並列処理が多いため、システムの構成は必然的にマルチプロセッサーとなった。下の画像がその概略図であるが、I/Oチャンネルとメモリーがそれぞれ独立して設けられ、これとは別に複数のプロセッサーが用意され、間が相互接続されるという仕組みだ。

画像の出典は“Pluribus-An Operational Fault-Tolerant Multiprocessor”。

これをもう少し細かく示したのが下の画像で、プロセッサーバス、メモリーバス、I/Oバスという3種類のバス(=それぞれの筐体)に、それぞれ目的のカードが装着される。バス同士はBus Couplerと呼ばれるI/Fで接続される形だ。

画像の出典は“Pluribus-An Operational Fault-Tolerant Multiprocessor”。

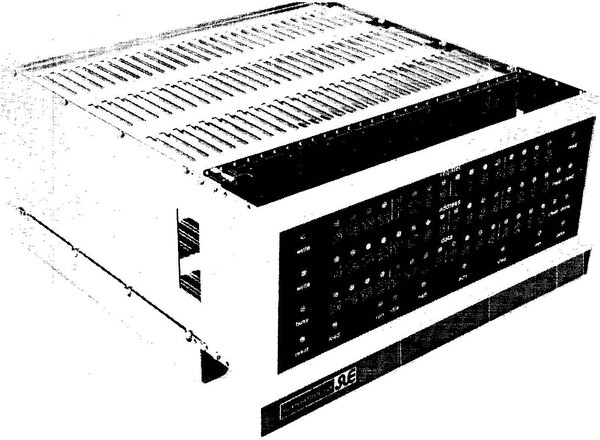

プロセッサーそのものは汎用である。利用したのはLockheed Electronicsの16bitシステムであるSUE(System-User-Engineeredの略)で、INFIBUSと呼ばれるパラレルバスにCPUやメモリー、I/Oなどを装着して構成するもので、構造的にはAltair 8800とあまり変わらない。

画像の出典は“SUE Computer Handbook”。

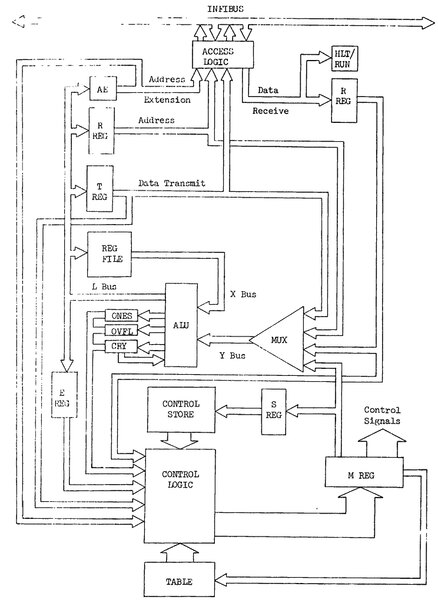

このSUEで利用されるプロセッサー「SUE Model 1110」は、16bitの汎用的なものだが、命令セットはDECのPDP-11互換である。

画像の出典は“Emulation of the PDP-11 instruction set on the Lockheed SUE processor”。

動作速度は不明だが、すべての命令はアクセス時間60ナノ秒のROMに格納されるマイクロコード方式なので、クロックそのものは逆算すると16.67MHzほどだろう。性能はそれを示す資料が見当たらないのだが、当時としてはそこそこの範疇だったと思われる。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ