今回のスーパーコンピューターの系譜は、GPUを使ったアクセラレーターの話である。GPUを使ったアクセラレーターといえば、まずNVIDIA、ついでAMD、最後にインテルあたりがぱっと思いつくと思う。

他にもARMやImagination Technologyも広義のアクセラレーターとしてはやはり名乗りを挙げているし、細かいところではVivante Corporationもこれに含まれるが、これらのベンダーは今のところモバイル向けSoC用のGPU/GPGPUを提供しており、HPCの枠からは外れるのでと除外すると、この3社が一番有名である。

CSX600

だが、GPUを使ったアクセラレーターとして一番最初に名乗りをあげたのはClearSpeed Technologyである。ClearSpeedのCSX600は、国内では東京工業大学のTSUBAME 1.0にも採用されたので、ご存知の方も多いかと思う。ただし「あれってGPUだっけ?」と思われる方もいると思うので、今回はこのClearSpeedの話をしよう。

幻のビデオカード

「FUZION 1」

ClearSpeed Technologyはイギリスに本拠を置くファブレス企業だが、その前身はPixelfusion plcという、やはりロンドンに本拠地を置くファブレスのグラフィックベンダーである。

1999年8月のHot Chips 11で同社は“Massively Par allel Comput ing on the FUZION Chip”という講演を行なっており、1999年にはFUZION 1という製品を発表することを明らかにしている。

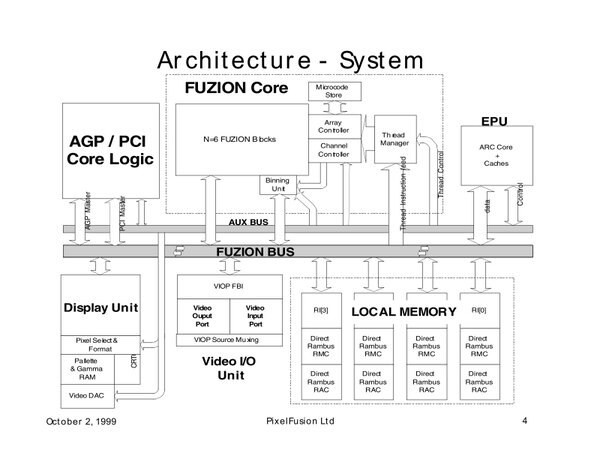

そのFUZION 1の内部構造が下の画像だ。“AGP/PCI Core Logic”や“Display Unit”、“Video I/O Unit”といった存在が辛うじてビデオカードらしいことを主張しているが、逆に言えばビデオカードらしい部分はこれだけで、肝心のFUZION CoreやLocal Memoryを見ると全然ビデオカードらしくない。

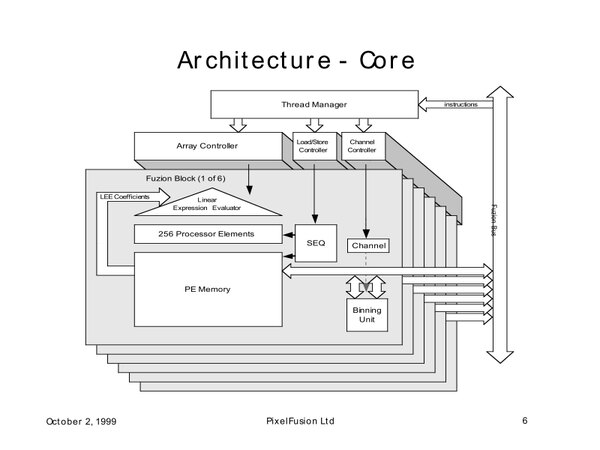

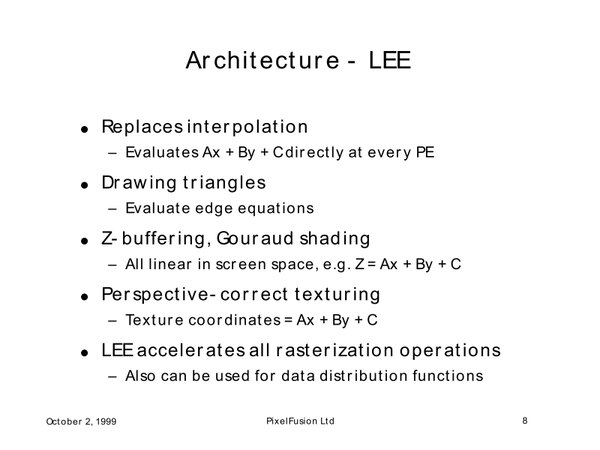

FUZION Coreの内部がこちらであるが、6つのFuzion Blockがそれぞれ256のPE(Processor Element)とLocal Memoryを持ち、この256個のPE毎に1つのLEE(Linear Expression Evaluator)を持つ、というおもしろい構造である。

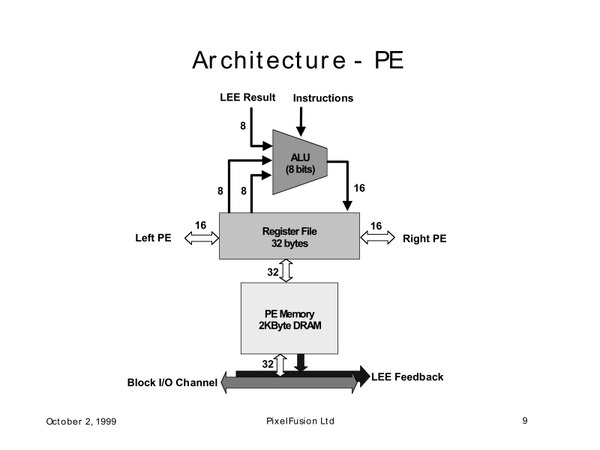

LEEの話は後にして先にPEの構造を下の画像に示す。各々のPEは8bitのALUで構成され、32個のLocal Registerを利用できる仕組みだ。

また各々のPEは2KBのメモリーを持つことができる。PE同士は相互に接続されており、連携して作業ができるようになっている。要するにFUZION 1は小規模ながらMPP(Massive Parallel Processing:超並列)の構造を持っているわけだ。

ではLEEはなにをやるかというと、より複雑な計算である。直線の補完やポリゴンの塗りつぶし、シェーディングやZ-Bufferingなど、複数の頂点にまたがる処理がLEEの作業範疇だとしている。

ちなみにこのFUZION 1は、0.25μmプロセスを利用してダイサイズは500mm2以上、消費電力は35W、7000万トランジスタという構成で、しかもeDRAMを使う関係でUMC/USICのみで製造できることになっていた。

性能(予測値)は以下のとおりで、演算性能こそ異様に高いが、肝心のグラフィック性能があまりたいしたことがない。

- 1.5T 8bit演算/秒(Multiply and Add)

- 600GB/秒 on chip DRAM Bandwidth

- 1.2TBytes/秒 PE bandwidth

- 3GFLOPS Processing(IEEE互換)

- 7GMACs(16bit×16bit)

- 150M 3D Transformations/秒

- 50M Triangles/秒

当初の予定ではテープアウトが1999年10月、最初のシリコンは1999年12月初頭、これを搭載した最初のボードの製造が2000年第1四半期、システム検証とOpenGL/Direct3D対応ドライバーの準備ができるのは2000年第2四半期、という勇ましいロードマップを立てていたが、これを搭載したボードが世の中に出ることはなかった。

1999年といえばNVIDIAがNV10ことGeForce 256をリリースした年であるが、そのNV10は0.22μmプロセスを使いトランジスタ数は1700万、ダイサイズは111mm2でしかなかった。

消費電力はわからなかったが、ファンは必須といいつつそう大きいものではなかったから、35Wよりはるかに少ないのは間違いない。

しかもNV10にはハードウェアT&Lを搭載していたが、FUZION 1にはその機能もない。FUZION 1そのものはコンシューマー向けというよりもワークステーション以上を指向した製品風だったため、必ずしもGeForceと競合はしないが、価格/性能比を考えたらどう考えても勝ち目はなかっただろう。

→次のページヘ続く (PixelFusionがプロセッサー製造ビジネスに転換)

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ