SOIベースのプロセッサー「Cell」

前回のFinFETで、インテルのプロセスに関する技術の目玉はほぼ一通り解説したが、もっと広範囲に半導体製造業界一般で使われている、または使おうとしている技術がいくつかある。

特に、次回解説予定のNTV/STV(Near Threshold Voltage/Sub Threshold Voltage)技術は、部分的にそれを取り入れようとした製品が「Quark X1000」という形で製品化されているが、本来はもっと先に投入されると予想される技術である。

AMDやIBMでは使われている

SOI(Silicon On Insulator)

今回はあえてインテルが背を向けて使おうとしない、SOI(Silicon On Insulator)について解説する。SOIはIBMが1999年にまずPowerPC向けに採用、これをAMDが全面的に採用し、同社の130~32nmのプロセスはすべてSOIをベースとしたものになっている。

ほかにもIBMと東芝とソニー・コンピュータエンタテインメントが共同で製造したCell Processorや、GLOBALFOUNDRIESのプロセスを使ったFreescaleのSoCがやはりSOIベースである。また、STMicroelectronicsは28nmのSOI技術を開発し、これを使ったアプリケーションプロセッサーを自社ファンダリーで製造するほか、この技術をGLOBALFOUNDRIESにライセンス供与している。

国際半導体技術ロードマップ(ITRS)においても、SOIは大分前から「実現すべき技術」扱いになっており、特にFinFETを実現した今となっては、もはや嫌うべき積極的な理由があまりない状態である。が、そのあたりを説明する前にまずはSOIという技術そのものについて説明したい。

SOIの仕組み

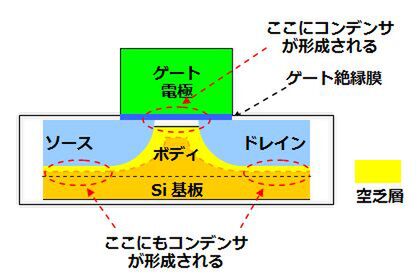

さて、まずはおなじみのトランジスター構造図であるが、下図はややこれまでと違う構図になっている。これまでは説明しなかったが、FETが動作するとき、その内部には空乏層(欠乏層という場合もある)と呼ばれる領域ができる。下図の黄色い部分がこれだ。

トランジスターの構造図

例えばNMOSの場合、ドレインとソースはN型半導体、ゲートの下に位置するボディ部はP型半導体のNPN構造である。ここでゲートに電圧をかけると、PN接続(N型半導体とP型半導体が接する部分)では電子と正孔が結合する結果として、正孔が存在しない領域が発生する。これが空乏層と呼ばれるものだ。

物理的には、空乏層はP型半導体(シリコン基板にホウ素などをイオンビームで打ち込むなどしてP型の物性を持たせた領域)ながら、内部的には絶縁体として作用することになる。

空乏層ができるとなにがまずいかというと、P型半導体のボディ部の下はそのままシリコン基板になっているわけで、結果としてベースやドレインとシリコン基板の間に電位差があり、かつ間に絶縁層が挟まれることで、ここにもコンデンサーが形成されることになる。

これは「トランジスタの寄生容量」という名前で知られている現象であり、これがあると電力が余分に食われたり、トランジスタの速度そのものが遅くなったり、といった問題が出てくる。

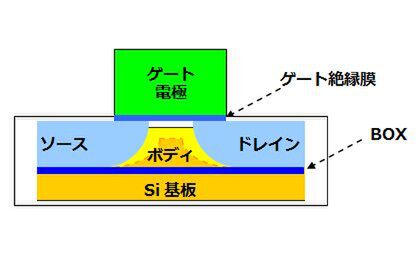

トランジスタの寄生容量を防ぐためにはどうしたらよいか、という答えが「ボディとシリコン基板を分離してしまえば良い」である。下図がそれで、FD-SOI(Fully-Depleted SOI:完全空乏型SOI)と呼ばれる方式の仕組みである。

FD-SOIの仕組み

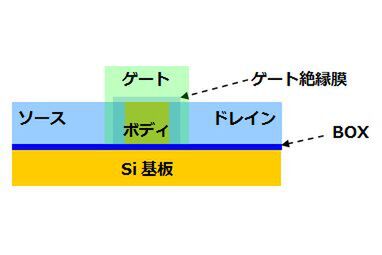

PN接続をしている部分があるから寄生容量が発生するのであって、ベースやドレインとボディが接する部分を最小限にすることで、大幅に寄生容量を減らせる。BOXというのはBuried OXide(埋め込み絶縁膜)を意味する。このFD-SOIは、FinFETと非常に相性が良い。というのは、FD-SOIをベースにFinFETを構成した場合、その構造は下図のようにシンプルになるからだ。

FD-SOIをベースにFinFETを構成した場合

もちろんこの場合でも、ソース/ドレインを成すNMOSとPMOSのボディ部はつながっているためPN接続は起きるわけだが、ここは寄生容量というよりはトランジスタのスイッチングにそもそも必要となる容量だから問題はない。

また、それ以外の部分は一切接していないので、他の部分ではPN接続はなく理論上空乏層が発生しない。前回「現在でもFinFETは原理的にSOIと相性が良い」と書いたのは、このことである。

そのFD-SOIの構造は、以下のメリットをもたらしている。

- 動作電圧を幅広く選べるため、低消費電力から高速動作まで、さまざまな特性を選びやすい。また低消費回路にも、ダイナミック回路をフルに生かした高速回路にも向いた特徴がある

- 高抵抗基板を利用可能で、RF回路やアナログ・デジタル混載回路に向いている

- 特性をそろえやすい(前提条件あり)

- 宇宙線などの影響によるエラーに強い

そんな素晴らしいFD-SOIであるが、なかなか普及しなかった。現在FD-SOIを量産プロセスで提供しているのは唯一STMicroelectronicsのみであり、あとは研究室レベルの話に留まっている。なぜなら、FD-SOIに対応したウェハーの製造が難しく、コストが非常に高いためである。

この連載の記事

-

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 -

第757回

PC

「RISC-VはArmに劣る」と主張し猛烈な批判にあうArm RISC-Vプロセッサー遍歴 - この連載の一覧へ