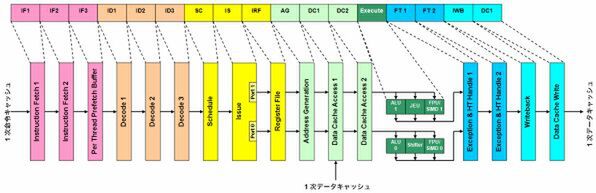

アウトオブオーダー方式のパイプラインだと、実行ユニットの処理結果はそのまま「Re-Order Buffer」に戻されて、命令完了処理が行なわれる。しかしAtomはインオーダー方式なので、処理のあとには命令完了処理が必要になる。まず「FT1」「FT2」ステージは、実行結果による例外処理のハンドリングや、ステータスレジスタなどの更新をスレッドごとに行なう。

それに続く「IWB」は、更新されたRegister Fileを書き出す。レジスタ間演算の場合、Register Fileの書き出し先は別のレジスタになるので、このステージで処理は終了する。演算結果をメモリーに書き出す場合は、さらに「DC1」ステージに移る。これはデータキャッシュへの書き出しである。これでやっとパイプライン終了である。

このように、Atomのパイプラインステージ全体は、16ステージと結構長めである。ただし、アウトオブオーダー方式のパイプラインなら、AG/DC1/DC2ステージがパイプラインに組み込まれることはない※2。Executeに続く部分も、Re-Order Bufferの後処理としてパイプライン外で処理される。これらを考慮すると、実質的にはAtomも10段程度のパイプラインとなり、とりたてて長くはない。

※2 データキャッシュからのフェッチをスケジューラーの中で待つため。

タイトすぎて性能向上が困難

22nm世代では別アーキテクチャーに?

当時は鳴り物入りで登場したAtom。しかし前述のとおり、一応2命令同時実行の実行ユニットを持っているとは言え、実質は1命令/サイクルの処理しかできなかった。3命令同時実行のPentium Mと比較すれば3分の1で、4命令同時実行のCore 2以降と比べればさらに性能は劣る。ラフに言えば、2GHz駆動のAtomと600MHz駆動のPentium Mが大体同程度となるので、「2GHz」という数字に期待を持っていた消費者の期待を裏切ることになったのは、インテルが大々的にAtomをアピールしすぎた反動もあったのかもしれない。

前回でも触れたとおり、インテルの45nm SoCプロセスは期待された性能を実現できず、そのうえ32nmへの移行も難航した。そのため長くAtomは性能を改善できないままラインナップだけ増やすことになる。消費者から「Atomでは……」と言われるようになってしまったのは、可哀想でもある。本来はもう少しアグレッシブに性能改善してゆくはずだったのだが、そうしたプランも先送りになってしまった。

Atomの設計があまりにタイトすぎて、性能を上げるためには内部の大改造が必須となることも、性能向上が進まない要因であるだろう。2命令同時実行に最適化しきった関係で、例えば命令発行ポートと実行ユニットを追加して3命令同時実行にするのは、現在のAtomの設計では至難の業だ。また、命令フェッチの帯域が現状でぎりぎりなので、仮に3命令を発行しても性能は出そうにない。だからといってここにまで手をいれると消費電力がぐわっと増えることは目に見えている。

インテルは22nm世代のAtomである「Silvermont」で、新アーキテクチャーを導入すると公表している。これが現行のインオーダー方式を継承したものか、それともAMDの「Bobcat」(AMD E/CのCPUコア)のようにアウトオブオーダーを使うものか、まだ判然としない。時間的に言えば、2008年あたりからもう一度フルスクラッチで新CPUの設計を始めても、Silvermontには十分間に合う。筆者は今回解説したパイプラインは現行Atomまでで、Silvermontはアウトオブオーダーを採用するのではないかと考えている。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ