一連のインテルのメインストリーム製品に関しては、前回の「Haswell」までで解説が終わった。CPUパイプラインの進化を辿るシリーズの締めくくりとして、2つほど「その他」のインテルCPUについて解説したい。ひとつめは、「Pentium 4」」シリーズで投入された「NetBurst Architecture」である。

「20段のパイプライン」と称する

Netburst Architectureの中身

2000年当時、180nmプロセス「Coppermine-T」コアの「Pentium III」が1.13GHz止まりだったのに対して、同年発表された「Willamette」こと初代Pentium 4は、180nmプロセスで2GHz駆動を実現した。同一周波数での性能はPentium IIIに及ばないものの、より高い動作周波数をサポートすることで、トータル性能でPentium IIIを圧倒することで性能改善をはたした(関連記事)。続く130nmプロセスの「Northwood」では、動作周波数は最大3.4GHzに達し、順調に性能を上げることに成功した。

ちなみに、Pentium ProことP6のアーキテクトの1人であるロバート P.コルウェル(Robert P.Colwell)氏の著書「The Pentium Chronicles」によれば、Willametteの開発は1994年あたりに始まったようで、開発開始から製品化まで6年近くかかったことになる。もっとも、Pentium Proも開発開始は1990年、製品出荷が1995年末であった。まったく新規にアーキテクチャーを開発する場合、俗に言われる「4年程度」では、まったく足りないということかもしれない。

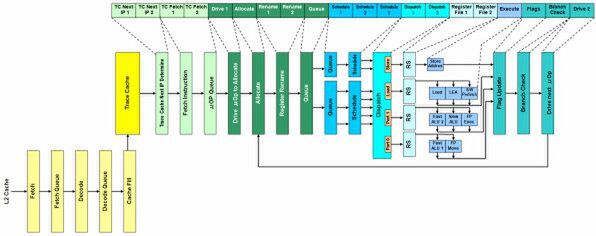

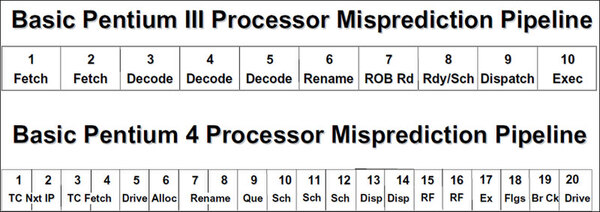

そのNetburst Architectureだが、よく知られているようにパイプライン段数は20段にも及ぶ。ただし、この20段というのはあまり正確ではなく、トータルではもう少し多い。よく20段と称される数字の根拠が下のスライドだが、実はこれがパイプラインのすべてではないからだ。

だがまずは20段の解説から始めよう。Netburst Architectureの特徴は「Hyper Pipeline」と呼ばれるもので、従来ならば1ステージで済ませる分を、複数ステージに分割するというものだ。これにより、1ステージの処理に必要な時間が短縮でき、結果として高速動作が可能になる。そのため、実質的なステージ数は12段ほどとなる。

最初の「TC Next IP」は、Trace Cacheから次の「命令の位置」を確定するステージだ。これに2サイクルを要している。ここで確定した次の命令を、Trace Cacheから取得するのが、それに続く「TC Fetch」である。TC Fetchで取得した命令は、いったん「μOp Queue」に格納される。実を言えば、このTC Next IP1から「TC Fetch 2」までの4ステージが、唯一インオーダー実行される部分である。ここから先はアウトオブオーダー実行になる。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ