メモリー編の途中であるが今回は予定を変更して、5月4日(現地時間)にインテルが発表した、22nmプロセスの「三次元トライゲート(Tri-Gate)・トランジスター」について解説したい。とは言っても、いきなり「トライゲートとはなんぞや」の話をしてもわけがわからないと思う。まずは基礎となるトランジスター(FET、電界効果トランジスター)の構造から説明しよう。

トランジスターの微細化と高速化の理屈をおさらい

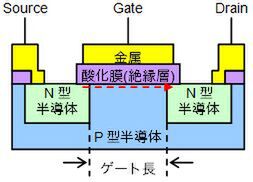

図1は回路図に出てくるFETの構造である。これは「NMOS型」というタイプのFETであるが、この動作原理をごく単純化して説明すると、ソース(Source)とゲート(Gate)の間の電圧を変化させると、これに連動する形でソース/ドレイン(Drain)間の電流が変化する、というものだ。つまり電圧を変化させることで、ソースからドレインへの電流をオン/オフできるという仕組みである。

図1 電界効果トランジスターの構造

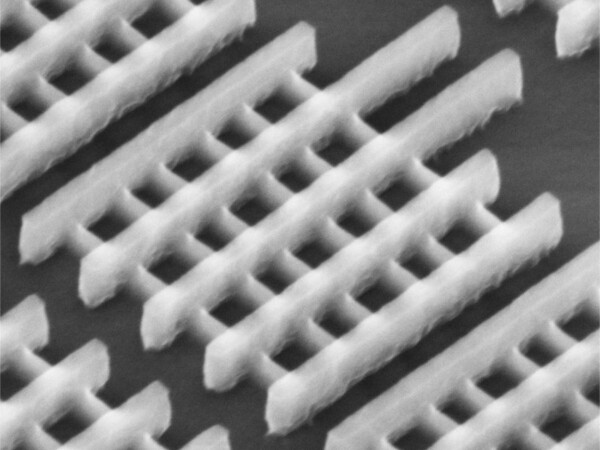

このNMOS型のFETの構造を、側面から断面図の形で示したのが図2である。ソース/ゲート間の電圧を変化させると、それにともなって電流が赤い破線のように、ソースからドレインへと流れるという仕組みだ。この基本的な構造そのものは、初期のCMOSから最新のトライゲートまでまったく同じと考えていい。

図2 トランジスターの側面図

ところが、半導体製造技術の進化によってトランジスターの構造が微細化していった結果、多くの問題が出てくるようになった。初期の数μmサイズの製造プロセスから180nmあたりまでは、プロセスを微細化するほどトランジスターは高速に動作して消費電力が減っていた。

物理的なサイズも小さくなるから、同じ回路ならば半分のダイサイズで製品が作れるし、ダイサイズを同じにすれば2倍のトランジスターが利用できるから、その分高機能や高性能にできる。180nmあたりまでは、単にプロセスを微細化するだけで皆がハッピーになれた。この傾向が怪しくなるのは、130nmあたりからだ。そして90nmプロセスでは、微細化にともなう副作用が大きな問題として出てくるようになった。

そもそも、なぜ微細化すると高速化や省電力化できるのか? それは微細化にともないゲート長の間隔が狭まったことに起因する。ゲート長というのは、ソースとドレインの2つのN型半導体の間の距離(NMOSの場合)のことだが、これが長いと当然ながら抵抗が大きいので、高い電圧をかけないと電流が流れないし、距離が長いから伝達遅延も増える。

逆に距離が短くなれば抵抗が減るので、それほど電圧をかけなくても電流が流れるようになる(よって消費電力も減る)。伝達遅延は距離に比例するから、ゲート長を縮めれば遅延も減り、結果として高速で動作する。

このあたりは、水道管の蛇口をイメージするとわかりやすい。昔は凄く大きな蛇口だったのでパッキングも分厚く、蛇口を目一杯捻らないと水が出なかった。そこで蛇口を小型化して、かつパッキングも薄くしたことで、蛇口をちょっと捻ると水が出てくるようになった、というイメージである。ところが、ある限度を超えて小型化した結果、今度は常に水が漏れる状態になってしまったわけだ。

この連載の記事

-

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 -

第757回

PC

「RISC-VはArmに劣る」と主張し猛烈な批判にあうArm RISC-Vプロセッサー遍歴 - この連載の一覧へ