メモリー編2回目では、DRAMから「EDO DRAM」までの進化を説明した。3回目ではそれに続く「SDRAM」の進化を解説したい。

RAS/CASをクロック信号で置き換えたSDRAM

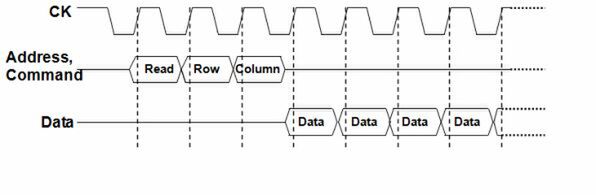

連載94回でも触れたが、SDRAMでは信号線にクロック信号が追加され、これに合わせてデータ転送が行なわれるようになった。図1はその大雑把なリードサイクル図である。

前回も掲載したEDO DRAMの図2と見比べればわかるが、SDRAMでは「RAS/CAS」の信号線が必要ない。EDO DRAMまでは、アドレスがどのタイミングで送られるかを判断するために、RAS/CASを独立した信号線として必要だった。

SDRAMではクロック信号の立ち上がりでアドレスが送られる仕組みになっているので、RASやCASといった信号線でタイミングを取る必要がなくなった。これによるメリットは2つある。まずメモリーコントローラーの側のメリットとして、DRAMのタイミングに合わせて細かく信号線の上げ下げをする必要がなくなったことが挙げられる。

ちょっと込み入った話になるが、CPUのみならず、チップセットやそのほかの周辺回路を含む大規模なロジック回路は、「同期回路」と呼ばれる方式で設計されるのが普通だ。これはクロック信号に合わせてロジック回路の中の細かいブロックが動作し、ブロック間でデータのやり取りを行なう方式である。

ところがEDO DRAMまでは、信号線がクロック信号と無関係なタイミングで上げ下げされることになりがちで、これを標準的な同期回路で処理するのは面倒だった。それがSDRAMになると、メモリーの信号そのものが同期信号になるから、難しい問題もなくメモリーコントローラーを同期回路で設計できるようになった。

一方メモリーの側も、これによって結果的に高速化が可能になった。というのは、SDRAMでは内部の回路を(CPUなどと同じく)パイプライン化することが可能になったからだ。また同時にパイプライン化により、アドレスバスをコマンドバスと共用にすることが可能になった。

この連載の記事

-

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 -

第757回

PC

「RISC-VはArmに劣る」と主張し猛烈な批判にあうArm RISC-Vプロセッサー遍歴 - この連載の一覧へ