今回は久しぶりにCPUロードマップの話題を取り上げよう。去る11月9日、AMDは「2010 AMD Financial Analyst Day」を開催した。このイベントは金融系のアナリストに向けて、自社の経営状態のレポートや今後の製品展開を含む業績予測、および自社の経営方針などを説明するという、株式上場会社にとっては重要なイベントである。

同時にこのイベントは、同社の今後の製品ロードマップ展開を示してくれるという観点で、IT業界/プレス関係者にとっても重要なイベントである。そんなFinancial Analyst Dayで2011年における製品ロードマップの概略が示されたので、まとめてご紹介したい。

なお、2011年2月にIEEEの主催する国際会議「ISSCC」(International Solid-State Circuits Conference)が開催される予定だが、開催に先立って講演プログラム一覧が公開された。この情報で少しだけ「Bulldozer」の概略もわかったので、こちらもあわせてご紹介しよう。

AMDの次世代CPUコア Bulldozer

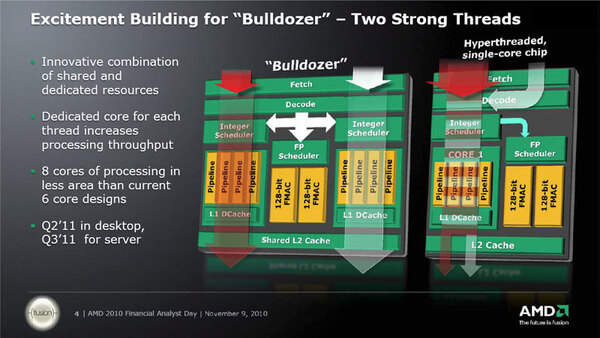

まずはBulldozerコアの話題から始めよう。Bulldozerは2つの「CPUコア」と、コアで共有されるフェッチ/デコードユニット、同じく共有のFP(浮動小数点演算)ユニットを持ち、これをひとつの「CPUモジュール」として取り扱うという、ちょっと独特な構造になっている。

FPユニットそのものは、基本的には128bit幅のものが2つ並んでいて、これが2つのコアで共有される。各FPユニットのピークにおけるクロックあたりスループットそのものは、従来の「K10」(Phenom)ベースと変わらないが、拡張命令「AVX」を含む256bitのFMAC命令の場合は、2つのFPユニットが連動して動く形となる。

HPC系のような科学技術計算を大量に行なわせる場合を除くと、すべてのCPUでFPUがフルに使われるというケースは希である。そこでFPUを共有構造にすることで、FPUを使うCPUはより高いスループットを得られるし、FPU自身の利用効率改善にもつながる、というのがこのアイディアである。

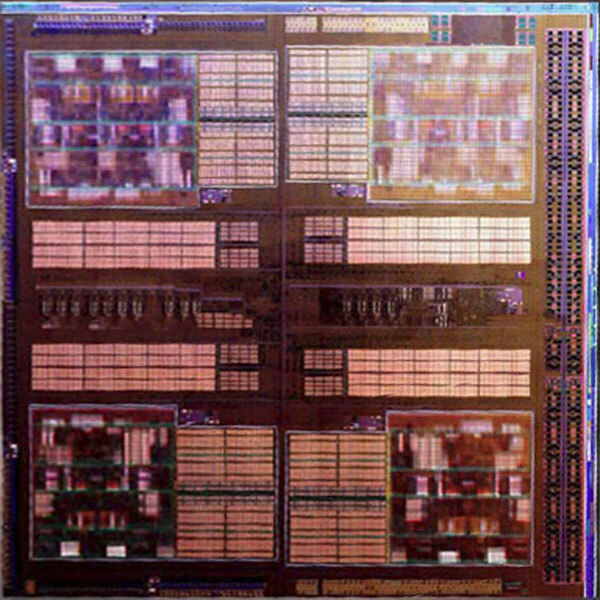

さてこのBulldozerであるが、今回は珍しくコアの写真がプレゼンテーションで掲載されたものの(写真左)、拡大してみると明らかにおかしい(写真右)。

右の写真は歪みを取った上で、(縦横比が不明なので)とりあえず600×600ドットに拡大したものだ。まず上下でコア(モジュール)のサイズがまったく異なっているし、そこにつながっていると思しき2次キャッシュのサイズも異なる。右上のモジュールは内部が比較的透けて見えるが、そのほかのダイは妙にぼけているのも気になる。そもそも下半分のモジュールは、上のモジュールと違うように見える。

ここまで違っていると、適当にでっち上げたフェイクな写真であることは間違いないだろう。ちょっと引き伸ばしただけでそれとわかるような写真をわざと出してきたあたりは、「製品ラウンチまで正式写真はお預け」という、AMDの悪戯っぽいメッセージを感じる。

この連載の記事

-

第768回

PC

AIアクセラレーター「Gaudi 3」の性能は前世代の2~4倍 インテル CPUロードマップ -

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 - この連載の一覧へ