TLBはページテーブルエントリのキャッシュ

キャッシュ同様に階層化も進む

だが、メモリーにページテーブルを置くとなると、今度は「煩雑にアクセスが発生した場合のレイテンシーの大きさ」が問題になる。「メモリーアクセスをするためのAddress Translationに先立って、まず変換テーブルをメモリーから読み込む」というのは、実質メモリーアクセスの速度が半分に落ちるに等しい。特にCPUの動作周波数が上がると、このオーバーヘッドが無視できないものになってきた。

この問題に対する対策がTLBである。TLBは「PTE専用のキャッシュ」だ。格納されるのは「直前に利用されたPTE」のみであり、これを利用するのはAddress Translationのメカニズムのみである。

こちらも以前は1段のTLBで済んでいたのが、命令/データ用が分かれたうえ、最近では「2次TLB」もでてきた。これはOSが利用するメモリーの量が段々増えてきて、同時に利用されるPTEの数が増えてきた結果、TLBを増量しないとキャッシュが有効に効かなくなってきたためだ。だからといって、TLBのエントリを無闇に増やすと(1次キャッシュ同様に)TLBの検索そのものに時間が掛かるので、複数段構成にしようというわけだ。

ちなみにNehalem/WestmereベースのCore iシリーズの場合、その前のCore 2 Duo/Quadと比べると、TLBはちょっと複雑な構造になっている。

| Nehalem/Westmere | Core 2 Duo/Quad | |

|---|---|---|

| 1次命令TLB | 128エントリ/コア (64エントリ/スレッド) 4ウェイセットアソシエイティブ |

128エントリ 4ウェイセットアソシエイティブ |

| 1次データTLB | 64エントリ 4ウェイセットアソシエイティブ |

16エントリ 4ウェイセットアソシエイティブ +64エントリ 4ウェイセットアソシエイティブ |

| 2次TLB | 512エントリ 4ウェイセットアソシエイティブ |

なし |

利用する環境によって、必要とされるTLBの大きさは変わる。無尽蔵に大きなTLBを設ければ済む、というものではないことがおわかりいただけよう。ちなみにAMDの「K8」(Athlon 64)の場合、命令/データともに1次/2次TLBを持ち、さらに3次キャッシュが2次TLBとして動作できるような構造になっていた。今のNehalemコアのCore iシリーズなどよりも、遥かに大量のページを扱うことを想定した、非常にサーバー向けのアーキテクチャーと見ることもできよう。

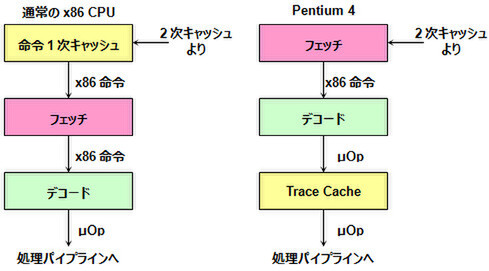

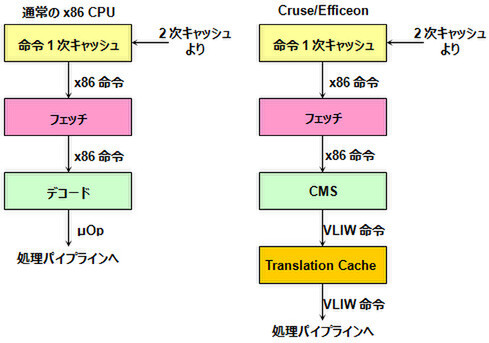

話を戻すと、このほかにx86系で使われた技術としては、「Pentium 4」の「トレースキャッシュ」(Trace Cache)と、Transmetaの「Crusoe」「Efficeon」で使われた「Translation Cache」が挙げられるが、これはどちらも似たものである。

Pentium 4のTrace Cacheは図2のように、パイプラインの構造を通常と変えて、デコード後の命令をキャッシュするようにしたものだ。これによりデコードの処理を実際の処理の流れから切り離すことに成功し、特にループ処理などで効果的に働くはずだった。しかし、肝心のPentium 4の処理性能の低さもあってその効果はほとんど評価されなかった。

ただ、インテルの内部ではこのTrace Cacheに一定の評価をしているようで、Nehalem/Westmereコアの「LSD」(Loop Stream Detector)を経て、まもなく登場する「SandyBridge」では、「Devoded μOps Cache」という形で、従来の1次キャッシュと並行して利用されることになる。

Crusoe/Efficeonもこれに似ている(図3)。これらは、x86をまず独自のVLIW命令に変換する(これをコードモーフィングと呼ぶ。詳細はこちらの記事を参照)。その際に、変換後のVLIW命令を一時的に蓄えるTranslation Cacheと呼ばれるものが存在した。

フェッチ/デコードをスケジューラー以降のパイプラインと分離して、間にキャッシュを挟むという方式は、x86に限らずほかのCPUアーキテクチャーでも見かける方式だ。しかし、以前は数命令分のバッファ程度、ということも多かった。ところが昨今では、性能改善のためにこのバッファを増やすケースが次第に増えてきている。将来的には、もっと多くのx86プロセッサーでも広く採用されていく可能性がある。

この連載の記事

-

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 -

第757回

PC

「RISC-VはArmに劣る」と主張し猛烈な批判にあうArm RISC-Vプロセッサー遍歴 - この連載の一覧へ