SIMDっぽくない命令の多いSSE3

SIMDな命令を増やしたSSSE3

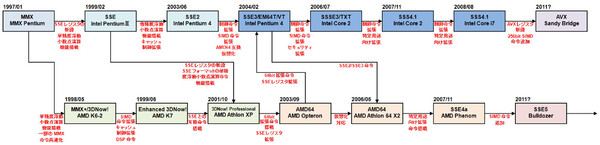

さて、この64bit対応と合わせて、インテルは「SSE3」を発表する。「PNI」(Prescott New Instruction)と称されたこの命令セットはSSE/SSE2と異なり、あまりSIMDっぽくない命令が増えたのが特徴である。実際新命令の内訳をまとめるとこうなる。

- FPUの高速化(1命令)

- SSEレジスターのLoad/Move/Duplicateの高速化(3命令)

- 128bitのUnalign Load(1命令)

- Packed Add/Sub(2命令)

- 水平加算(4命令)

- システム同期(2命令)

「水平加算」というのは、例えば図2(HADDPD、Packed Double-FP Horizontal Add)のように、レジスター間で演算するのではなく、レジスター内の要素同士で演算するというものだ。確かにあればあったで便利(同じ処理をSSE2でやるためには、一度XMMレジスターの値の入れ替えが必要だった)かもしれないが、「ないとどうしても困る」ほどでもないという類のものである。

むしろ、マルチスレッドプログラムでスレッド間の同期を取るのに便利なMonitor/MWAIT命令とか、整数とFPUの値を高速に変換するFISTTP(Store Integer and Pop from x87-FP with Truncation)の方が、SSE3の新命令として持てはやされる、といった状況になっていたものだ。

この状況は、続いて「Core 2 Duo」で導入された「SSSE3」でさらに顕著になった。SSSE3は「Supplimental SSE3」の略で、SSE3を補う命令といったところ。実際にSSSE3で追加された命令の内訳は以下のようになり、一応どれもSIMD風命令である。

- 水平加算/減算(12命令)

- 絶対値の評価(6命令)

- 乗加算(2命令)

- 乗算(2命令)

- 並べ替え(2命令)

- 符号反転(6命令)

- 右寄せ(2命令)

ただし、その内容はSSE3の延長にある。例えば水平加算で追加されたPHADDD命令は図3のような処理をするもので、図2のHADDPDを32bit対応にしたという趣きのものだ。こうした傾向はほかの命令にも共通で、その意味では「Supplimental」という接頭詞は極めて適切と言える。

ただし、「本当にこうした命令のニーズはあるのか?」という疑問が消えない命令拡張だったことも事実だ。SSE/SSE2をフルに使おうとすると、SSEレジスターの内容を入れ替えたり、置き換えたりという作業が頻繁に必要になる。そこでSSE3/SSSE3で置き換え処理を高速化したり、内容を入れ替えなくても処理できるような命令を追加して利便性を高めようという趣旨であった。

ところが今度は命令が無駄に多くなってしまい、ハンドアセンブルでプログラミングする場合はともかく、コンパイラーがこれらの命令をフルに使えるか疑わしいほどに命令が増えてしまった。この結果として、AMDはSSE2/SSE3に関しては、90nm世代のDual-Core K8(デュアルコア版のAthlon 64/Opteron)でサポートしたものの、SSSE3は「その必要性なし」としてサポートしないままとなる。

この連載の記事

-

第767回

PC

Lunar LakeはWindows 12の要件である40TOPSを超えるNPU性能 インテル CPUロードマップ -

第766回

デジタル

Instinct MI300のI/OダイはXCDとCCDのどちらにも搭載できる驚きの構造 AMD GPUロードマップ -

第765回

PC

GB200 Grace Blackwell SuperchipのTDPは1200W NVIDIA GPUロードマップ -

第764回

PC

B100は1ダイあたりの性能がH100を下回るがAI性能はH100の5倍 NVIDIA GPUロードマップ -

第763回

PC

FDD/HDDをつなぐため急速に普及したSASI 消え去ったI/F史 -

第762回

PC

測定器やFDDなどどんな機器も接続できたGPIB 消え去ったI/F史 -

第761回

PC

Intel 14Aの量産は2年遅れの2028年? 半導体生産2位を目指すインテル インテル CPUロードマップ -

第760回

PC

14nmを再構築したIntel 12が2027年に登場すればおもしろいことになりそう インテル CPUロードマップ -

第759回

PC

プリンター接続で業界標準になったセントロニクスI/F 消え去ったI/F史 -

第758回

PC

モデムをつなぐのに必要だったRS-232-CというシリアルI/F 消え去ったI/F史 -

第757回

PC

「RISC-VはArmに劣る」と主張し猛烈な批判にあうArm RISC-Vプロセッサー遍歴 - この連載の一覧へ