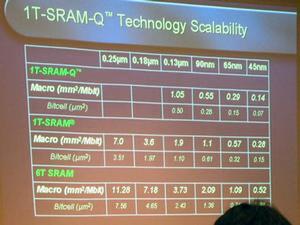

米MoSys社は16日、任天堂の家庭用ゲーム機『ゲームキューブ』などにも採用されている組み込み用SRAM技術“1T-SRAM”をより高集積化した“1T-SRAM-Q”を発表し、都内で記者説明会を開催した。一般的なSRAM(6トランジスター構成)に比べて4倍、1T-SRAM(1トランジスター構成)に比べても2倍の集積度になるという。製造プロセスは0.13μmおよび90nmの2タイプが用意され、将来は65nm/45nmプロセスルール版も計画されている。

|

| |

|---|---|---|

| MoSysの副社長兼IP部門本部長のマーク エリック・ジョーンズ氏 | (株)スピナカーシステムズの取締役ターンキー・IP本部本部長の片桐 徹氏 |

記者説明会には、MoSysの副社長兼IP部門本部長のマーク エリック・ジョーンズ(Mark-Eric Jones)氏と、同社日本総代理店を行なう(株)スピナカーシステムズの取締役ターンキー・IP本部本部長の片桐 徹氏が出席し、1T-SRAM-Qの優位性や製造技術、コストなどについて説明した。

まず、片桐氏が「現在、CPUなどの各種機能とメモリーを1チップ化したSoC(システム・オン・チップ)が主流になってきているが、求められるメモリー容量が増大するにつれて、現在では実装面積の半分以上をメモリーが占めるに至っている。“1T-SRAM-Q”を採用することで、これを30%台に抑えられるだろう」と1T-SRAM-Qの必要性を述べた。

|

| |

|---|---|---|

| 1T-SRAMの構造モデル | 1T-SRAM-Qの構造モデル |

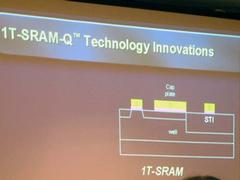

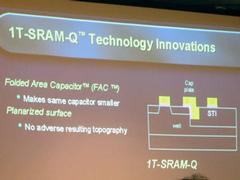

続いてジョーンズ氏が1T-SRAMとの違いを中心に、1T-SRAM-Qの技術説明を行なった。それによると、従来1T-SRAMにおいて大きな面積を占める、電荷を蓄えるためのキャパシタープレート(一種のトランジスター)を隣接するメモリーへの接続部“STI(Shallow trench isolation)”に畳み込む形で実装する“FAC(Folded Area Capacitor)”技術により、キャパシターの表面積(水平面積)を小さくすることができたという。この実装に際しては、STIに溝を作るためのマスク処理と酸化膜形成のエッチング処理が加わるものの熱処理工程はないので、ほかのトランジスターには影響は出ないという。製造コストはマスク処理1枚に1万ドル(約120万円)以下、追加工程に5%程度かかると見込まれる。また、実装面積の縮小以外のメリットとして、配線の短縮により高速化、省電力化が挙げられる、と説明した。

|

|---|

| 1T-SRAM-Q/1T-SRAM/6T-SRAM(従来のSRAM)の実装面積比較表 |

なお、2~3ヵ月中にMoSysの日本支社を設立予定であることも同時に発表された。また、同社は現在、自社でのメモリー製造/販売よりもパテントの提供が主要業態となっており、1T-SRAM-Qも国内の数社と話し合いを進めていること、自社生産については台湾ティーエスエムシー(TSMC)社をファブに利用することなどが公表された。